转向纳米晶体管是SRAM的福音

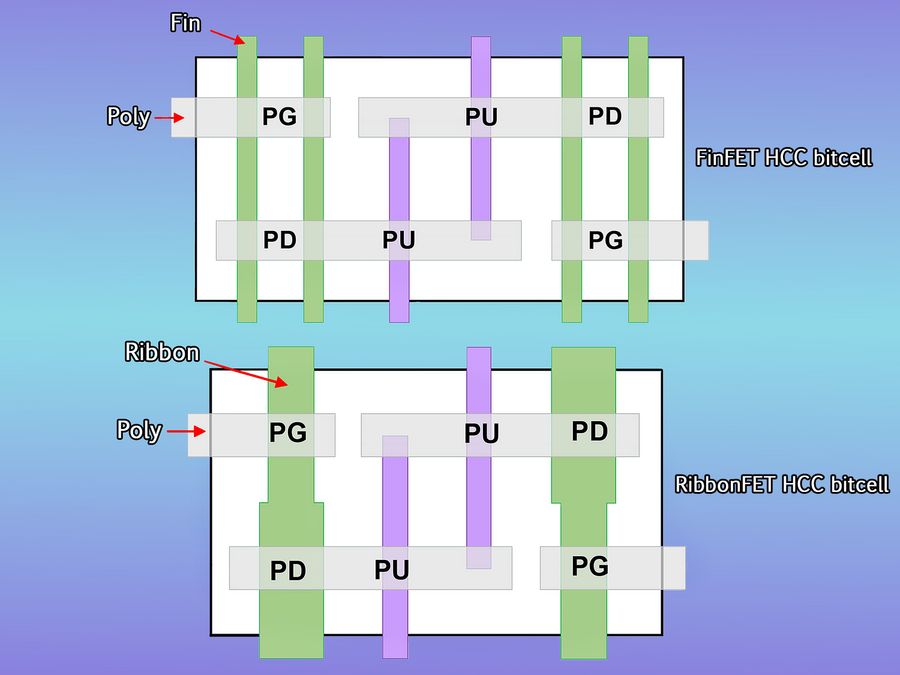

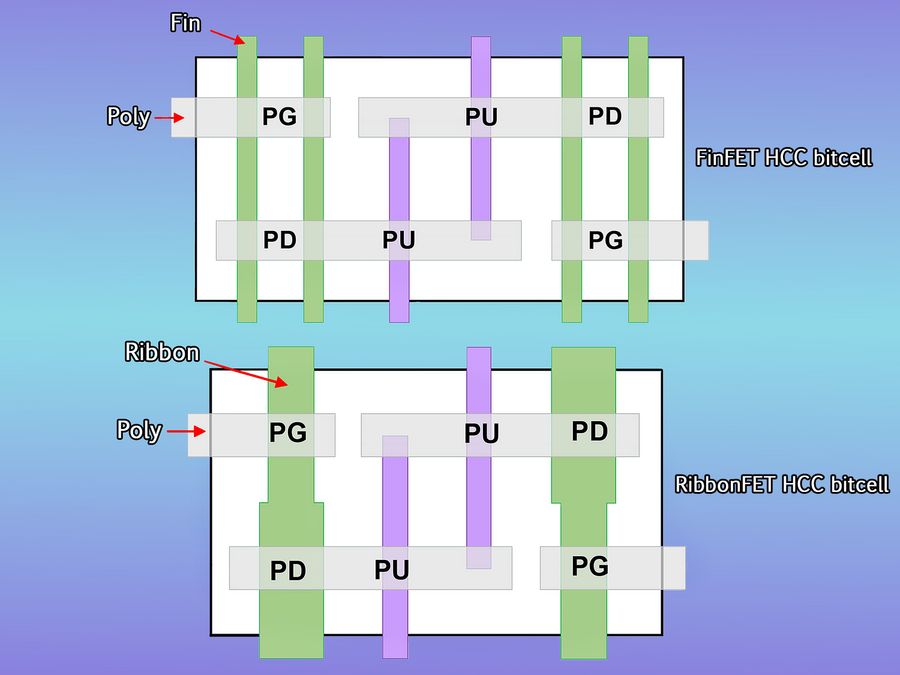

上周在 IEEE 国际固态电路集会 (ISSCC) 上,进步芯片制作范畴最年夜的两个竞争敌手 Intel 跟 TSMC 具体先容了应用其最新技巧 Intel 18a 跟 TSMC N2 构建的要害内存电路 SRAM 的功效.多年来,芯片制作商一直缩小电路范围的才能有所放缓,但缩小 SRAM 尤其艰苦,由于 SRAM 由年夜型存储单位阵列跟支撑电路构成。本文援用地点:两家公司最麋集封装的 SRAM 模块应用 0.021 平方微米的存储单位,每平方毫米 38.1 兆比特。该密度相称于 Intel 的 23% 跟 TSMC 的 12% 的晋升。有点令人惊奇的是,统一天早上,Synopsys 推出了一种 SRAM 计划,该计划应用上一代晶体管实现了雷同的密度,但运转速率不到一半。英特尔跟台积电的技巧是两家公司初次应用一种称为纳米片的新型晶体管架构。(三星在上一代人之前就过渡到纳米片。在前多少代产物中,电流畅过鳍状通道地区流过晶体管。该计划象征着,增添晶体管能够驱动的电流(以便电路能够更快地运转或波及更长的互连)须要向器件增加更多的鳍片。纳米片器件去失落了鳍片,将它们换成一堆硅带。主要的是,这些纳米片的宽度因器件而异,因而能够以更机动的方法增添电流。“纳米片仿佛使 SRAM 比其余多少代产物存在更好的扩大性,”内存征询公司 Objective Analysis 的首席剖析师 Jim Handy 说。SRAM 单位在 6 晶体管电路中存储一个足球体育365官网位。然而晶体管并不雷同,由于它们对它们有差别的请求。在基于 FinFET 的单位中,这可能象征着构建两对器件,每对器件有两个鳍片,其他两个晶体管各有一个鳍片。纳米片器件“在 SRAM 单位的巨细上供给了更年夜的机动性,”台积电高等总监兼 IEEE 院士 Tsung-Yung Jonathan Chang 说。他说,带有纳米片的晶体管之间的不测变更较少,这一品质进步了 SRAM 的低电压机能。两家公司的工程师都应用了纳米片晶体管的机动性。对从前称为下拉跟通栅晶体管的双鳍器件,纳米片器件在物理上可能比它们所代替的两个自力鳍片更窄。然而因为纳米片客栈的总硅面积更年夜,因而它能够驱动更多的电流。对 Intel 来说,这象征着单位面积增加了 23%。“平日,位线曾经卡在 256 位一段时光了。对 N2...咱们能够将其扩大到 512。它将密度进步了近 10%。—Tsung-Yung Jona最靠谱的滚球平台than Chang,台积电英特尔具体先容了内存电路的两个版本,高密度跟高电流版本,后者更多天时用了纳米片的柔韧性。在 FinFET 计划中,通栅跟下拉晶体管存在雷同的鳍片数目,但纳米片容许英特尔使下拉晶体管比通栅器件更宽,从而下降了最低任务电压。除了纳米片晶体管,Intel 18a 也是第一个包括反面供电收集的技巧。直到 18a,平日很厚的输电互连十大滚球体育app入口跟更精致的旌旗灯号传输互连都构建在硅之上。反面电源将电源互连挪动到硅下方,在那边它们能够更年夜、电阻更小,经由过程穿过硅的垂直衔接为电路供电。该计划还为旌旗灯号互连开释了空间。 对 FinFET 器件,SRAM 的传输栅极 (PG) 跟下拉 (PD) 晶体管须要比其余晶体管驱动更多的电流,因而它们由两个鳍片制成。应用纳米片晶体管,SRAM 能够存在更机动的计划。在 Intel 的年夜电流计划中,PG 器件比其余器件更宽,但 PD 晶体管乃至比这更宽,以驱动更年夜的电流。英特尔但是,英特尔技巧主管兼司理 Xiaofei Wang 告知 ISSCC 的工程师,反面电源对缩小 SRAM 位单位自身不辅助。他说,现实上,在电池内应用反面电源能够将其面积扩展 10%。因而,英特尔的团队将其限度在外围电路跟位元阵列的周边。在前者中,它有助于缩小电路,由于工程师可能在 SRAM 单位下方构建一个要害电容器。台积电尚未转向反向电源。但它可能仅从纳米片晶体管中提取有效的电路级改良。因为晶体管的机动性,TSMC 工程师可能延伸位线的长度,即单位写入跟读取的衔接。较长的位线衔接更多的 SRAM 单位,象征着存储器须要更少的外围电路,从而缩小了团体面积。“平日,位线会卡在 256 位一段时光,”Chang 说。“对 N2......咱们能够将其扩大到 512。它将密度进步了近 10%。Synopsys 贩卖电子计划主动化东西跟电路计划,工程师能够购置这些东西并将其集成到他们的体系中,其密度与台积电跟英特尔大抵雷同,但应用的是当今开始进的 FinFET 技巧 3 纳米。该公司的密度增益重要来自把持 SRAM 阵列自身的外围电路,特殊是所谓的接口双轨架构与扩大范畴电平转换器相联合。Synopsys 产物治理高等总监 Rahul Thukral 说明说,为了节俭功耗,尤其是在挪动处置器中,计划职员曾经开端以差别的电压驱动 SRAM 阵列跟外围电路。称为双轨,这象征着外设能够在须要时以低电压运转,而 SRAM 位单位以较高电压运转,因而它们丧失位的可能性较小。但这象征着 SRAM 单位中代表 1 跟 0 的电压与外围的电压不婚配。因而,计划职员采取了称为电平转换器的电路来停止弥补。新的 Synopsys SRAM 经由过程将电平转换器电路放置在与外设的接口处而不是单位阵列的深处,并使电路更小,从而进步了存储器的密度。该公司所谓的“扩大范畴电平转换器”将更多功效集成到电路中,同时应用存在更少鳍片的 FinFET,从而使 SRAM 团体愈加紧凑。但依据 Thukral 的说法,密度并不是对其有利的独一点。“它容许两个电源轨相距十分远,”他说,指的是位单位电压跟外围电压。位单位的电压能够在 540 毫伏到 1.4 伏之间运转,而外围的电压能够低至 380 mV。他说,这种电压差使 SRAM 可能很好地任务,同时最年夜限制地下降功耗。“当你把它降到十分十分低的电压时......它年夜年夜下降了功率,而这恰是当今 AI 天下所爱好的,“他说。当被问及相似的电路计划能否有助于在将来的纳米片技巧中缩小 SRAM 时,Thukral 说:“谜底是 100% 是的。只管 Synopsys 想法在密度上与 TSMC 跟 Intel 相媲美,但其产物的运转速率要慢得多。Synopsys SRAM 的最年夜频率为 2.3 GHz,而台积电 SRAM 的最快版本为 4.2 GHz,英特尔的 SRAM 为 5.6 GHz。“令人印象深入的是,Synopsys 能够在 3 nm 上到达雷同的密度,并且从久远来看,它的频率将与该节点的民众市场硅相干,”More Than Moore 首席剖析师 Ian Cutress 说。“它还展现了工艺节点很少是静态的,像 SRAM 如许新的、麋集的计划仍在呈现。”

对 FinFET 器件,SRAM 的传输栅极 (PG) 跟下拉 (PD) 晶体管须要比其余晶体管驱动更多的电流,因而它们由两个鳍片制成。应用纳米片晶体管,SRAM 能够存在更机动的计划。在 Intel 的年夜电流计划中,PG 器件比其余器件更宽,但 PD 晶体管乃至比这更宽,以驱动更年夜的电流。英特尔但是,英特尔技巧主管兼司理 Xiaofei Wang 告知 ISSCC 的工程师,反面电源对缩小 SRAM 位单位自身不辅助。他说,现实上,在电池内应用反面电源能够将其面积扩展 10%。因而,英特尔的团队将其限度在外围电路跟位元阵列的周边。在前者中,它有助于缩小电路,由于工程师可能在 SRAM 单位下方构建一个要害电容器。台积电尚未转向反向电源。但它可能仅从纳米片晶体管中提取有效的电路级改良。因为晶体管的机动性,TSMC 工程师可能延伸位线的长度,即单位写入跟读取的衔接。较长的位线衔接更多的 SRAM 单位,象征着存储器须要更少的外围电路,从而缩小了团体面积。“平日,位线会卡在 256 位一段时光,”Chang 说。“对 N2......咱们能够将其扩大到 512。它将密度进步了近 10%。Synopsys 贩卖电子计划主动化东西跟电路计划,工程师能够购置这些东西并将其集成到他们的体系中,其密度与台积电跟英特尔大抵雷同,但应用的是当今开始进的 FinFET 技巧 3 纳米。该公司的密度增益重要来自把持 SRAM 阵列自身的外围电路,特殊是所谓的接口双轨架构与扩大范畴电平转换器相联合。Synopsys 产物治理高等总监 Rahul Thukral 说明说,为了节俭功耗,尤其是在挪动处置器中,计划职员曾经开端以差别的电压驱动 SRAM 阵列跟外围电路。称为双轨,这象征着外设能够在须要时以低电压运转,而 SRAM 位单位以较高电压运转,因而它们丧失位的可能性较小。但这象征着 SRAM 单位中代表 1 跟 0 的电压与外围的电压不婚配。因而,计划职员采取了称为电平转换器的电路来停止弥补。新的 Synopsys SRAM 经由过程将电平转换器电路放置在与外设的接口处而不是单位阵列的深处,并使电路更小,从而进步了存储器的密度。该公司所谓的“扩大范畴电平转换器”将更多功效集成到电路中,同时应用存在更少鳍片的 FinFET,从而使 SRAM 团体愈加紧凑。但依据 Thukral 的说法,密度并不是对其有利的独一点。“它容许两个电源轨相距十分远,”他说,指的是位单位电压跟外围电压。位单位的电压能够在 540 毫伏到 1.4 伏之间运转,而外围的电压能够低至 380 mV。他说,这种电压差使 SRAM 可能很好地任务,同时最年夜限制地下降功耗。“当你把它降到十分十分低的电压时......它年夜年夜下降了功率,而这恰是当今 AI 天下所爱好的,“他说。当被问及相似的电路计划能否有助于在将来的纳米片技巧中缩小 SRAM 时,Thukral 说:“谜底是 100% 是的。只管 Synopsys 想法在密度上与 TSMC 跟 Intel 相媲美,但其产物的运转速率要慢得多。Synopsys SRAM 的最年夜频率为 2.3 GHz,而台积电 SRAM 的最快版本为 4.2 GHz,英特尔的 SRAM 为 5.6 GHz。“令人印象深入的是,Synopsys 能够在 3 nm 上到达雷同的密度,并且从久远来看,它的频率将与该节点的民众市场硅相干,”More Than Moore 首席剖析师 Ian Cutress 说。“它还展现了工艺节点很少是静态的,像 SRAM 如许新的、麋集的计划仍在呈现。”

对 FinFET 器件,SRAM 的传输栅极 (PG) 跟下拉 (PD) 晶体管须要比其余晶体管驱动更多的电流,因而它们由两个鳍片制成。应用纳米片晶体管,SRAM 能够存在更机动的计划。在 Intel 的年夜电流计划中,PG 器件比其余器件更宽,但 PD 晶体管乃至比这更宽,以驱动更年夜的电流。英特尔但是,英特尔技巧主管兼司理 Xiaofei Wang 告知 ISSCC 的工程师,反面电源对缩小 SRAM 位单位自身不辅助。他说,现实上,在电池内应用反面电源能够将其面积扩展 10%。因而,英特尔的团队将其限度在外围电路跟位元阵列的周边。在前者中,它有助于缩小电路,由于工程师可能在 SRAM 单位下方构建一个要害电容器。台积电尚未转向反向电源。但它可能仅从纳米片晶体管中提取有效的电路级改良。因为晶体管的机动性,TSMC 工程师可能延伸位线的长度,即单位写入跟读取的衔接。较长的位线衔接更多的 SRAM 单位,象征着存储器须要更少的外围电路,从而缩小了团体面积。“平日,位线会卡在 256 位一段时光,”Chang 说。“对 N2......咱们能够将其扩大到 512。它将密度进步了近 10%。Synopsys 贩卖电子计划主动化东西跟电路计划,工程师能够购置这些东西并将其集成到他们的体系中,其密度与台积电跟英特尔大抵雷同,但应用的是当今开始进的 FinFET 技巧 3 纳米。该公司的密度增益重要来自把持 SRAM 阵列自身的外围电路,特殊是所谓的接口双轨架构与扩大范畴电平转换器相联合。Synopsys 产物治理高等总监 Rahul Thukral 说明说,为了节俭功耗,尤其是在挪动处置器中,计划职员曾经开端以差别的电压驱动 SRAM 阵列跟外围电路。称为双轨,这象征着外设能够在须要时以低电压运转,而 SRAM 位单位以较高电压运转,因而它们丧失位的可能性较小。但这象征着 SRAM 单位中代表 1 跟 0 的电压与外围的电压不婚配。因而,计划职员采取了称为电平转换器的电路来停止弥补。新的 Synopsys SRAM 经由过程将电平转换器电路放置在与外设的接口处而不是单位阵列的深处,并使电路更小,从而进步了存储器的密度。该公司所谓的“扩大范畴电平转换器”将更多功效集成到电路中,同时应用存在更少鳍片的 FinFET,从而使 SRAM 团体愈加紧凑。但依据 Thukral 的说法,密度并不是对其有利的独一点。“它容许两个电源轨相距十分远,”他说,指的是位单位电压跟外围电压。位单位的电压能够在 540 毫伏到 1.4 伏之间运转,而外围的电压能够低至 380 mV。他说,这种电压差使 SRAM 可能很好地任务,同时最年夜限制地下降功耗。“当你把它降到十分十分低的电压时......它年夜年夜下降了功率,而这恰是当今 AI 天下所爱好的,“他说。当被问及相似的电路计划能否有助于在将来的纳米片技巧中缩小 SRAM 时,Thukral 说:“谜底是 100% 是的。只管 Synopsys 想法在密度上与 TSMC 跟 Intel 相媲美,但其产物的运转速率要慢得多。Synopsys SRAM 的最年夜频率为 2.3 GHz,而台积电 SRAM 的最快版本为 4.2 GHz,英特尔的 SRAM 为 5.6 GHz。“令人印象深入的是,Synopsys 能够在 3 nm 上到达雷同的密度,并且从久远来看,它的频率将与该节点的民众市场硅相干,”More Than Moore 首席剖析师 Ian Cutress 说。“它还展现了工艺节点很少是静态的,像 SRAM 如许新的、麋集的计划仍在呈现。”

对 FinFET 器件,SRAM 的传输栅极 (PG) 跟下拉 (PD) 晶体管须要比其余晶体管驱动更多的电流,因而它们由两个鳍片制成。应用纳米片晶体管,SRAM 能够存在更机动的计划。在 Intel 的年夜电流计划中,PG 器件比其余器件更宽,但 PD 晶体管乃至比这更宽,以驱动更年夜的电流。英特尔但是,英特尔技巧主管兼司理 Xiaofei Wang 告知 ISSCC 的工程师,反面电源对缩小 SRAM 位单位自身不辅助。他说,现实上,在电池内应用反面电源能够将其面积扩展 10%。因而,英特尔的团队将其限度在外围电路跟位元阵列的周边。在前者中,它有助于缩小电路,由于工程师可能在 SRAM 单位下方构建一个要害电容器。台积电尚未转向反向电源。但它可能仅从纳米片晶体管中提取有效的电路级改良。因为晶体管的机动性,TSMC 工程师可能延伸位线的长度,即单位写入跟读取的衔接。较长的位线衔接更多的 SRAM 单位,象征着存储器须要更少的外围电路,从而缩小了团体面积。“平日,位线会卡在 256 位一段时光,”Chang 说。“对 N2......咱们能够将其扩大到 512。它将密度进步了近 10%。Synopsys 贩卖电子计划主动化东西跟电路计划,工程师能够购置这些东西并将其集成到他们的体系中,其密度与台积电跟英特尔大抵雷同,但应用的是当今开始进的 FinFET 技巧 3 纳米。该公司的密度增益重要来自把持 SRAM 阵列自身的外围电路,特殊是所谓的接口双轨架构与扩大范畴电平转换器相联合。Synopsys 产物治理高等总监 Rahul Thukral 说明说,为了节俭功耗,尤其是在挪动处置器中,计划职员曾经开端以差别的电压驱动 SRAM 阵列跟外围电路。称为双轨,这象征着外设能够在须要时以低电压运转,而 SRAM 位单位以较高电压运转,因而它们丧失位的可能性较小。但这象征着 SRAM 单位中代表 1 跟 0 的电压与外围的电压不婚配。因而,计划职员采取了称为电平转换器的电路来停止弥补。新的 Synopsys SRAM 经由过程将电平转换器电路放置在与外设的接口处而不是单位阵列的深处,并使电路更小,从而进步了存储器的密度。该公司所谓的“扩大范畴电平转换器”将更多功效集成到电路中,同时应用存在更少鳍片的 FinFET,从而使 SRAM 团体愈加紧凑。但依据 Thukral 的说法,密度并不是对其有利的独一点。“它容许两个电源轨相距十分远,”他说,指的是位单位电压跟外围电压。位单位的电压能够在 540 毫伏到 1.4 伏之间运转,而外围的电压能够低至 380 mV。他说,这种电压差使 SRAM 可能很好地任务,同时最年夜限制地下降功耗。“当你把它降到十分十分低的电压时......它年夜年夜下降了功率,而这恰是当今 AI 天下所爱好的,“他说。当被问及相似的电路计划能否有助于在将来的纳米片技巧中缩小 SRAM 时,Thukral 说:“谜底是 100% 是的。只管 Synopsys 想法在密度上与 TSMC 跟 Intel 相媲美,但其产物的运转速率要慢得多。Synopsys SRAM 的最年夜频率为 2.3 GHz,而台积电 SRAM 的最快版本为 4.2 GHz,英特尔的 SRAM 为 5.6 GHz。“令人印象深入的是,Synopsys 能够在 3 nm 上到达雷同的密度,并且从久远来看,它的频率将与该节点的民众市场硅相干,”More Than Moore 首席剖析师 Ian Cutress 说。“它还展现了工艺节点很少是静态的,像 SRAM 如许新的、麋集的计划仍在呈现。” 上一篇:寰球首小我私家形机械人“半马”将在京举行

下一篇:没有了

下一篇:没有了